[ad_1]

Enhancing electrical automobiles and power techniques with cutting-edge know-how to optimize efficiency and prolong lifespan.

Battery Administration Methods (BMS) play a pivotal position in high-end battery-powered functions like electrical automobiles and power storage techniques. Their main position is to safeguard the well being of all cells inside a battery pack, making certain optimum energy supply for the required software. Moreover, they act as a protecting defend, stopping cell injury and making certain each cell operates throughout the prompt circumstances set by the producer. This not solely ensures environment friendly efficiency but additionally prolongs the battery pack’s lifespan.

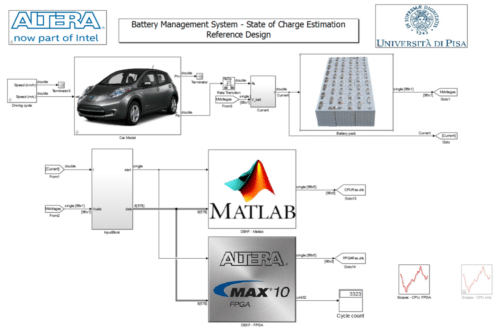

The Altera BMS Reference Design from Intel showcases find out how to estimate battery state of cost (SOC) on an FPGA-based real-time management system. This platform may be additional enhanced to include further BMS options like monitoring the battery’s state-of-health and making certain cost equalization, also called cell balancing. This design leverages a twin prolonged Kalman filter (DEKF) algorithm to find out SOC for as much as 96 cells, with the assistance of a MAX 10 growth package. FPGAs function versatile and potent platforms for BMS options. Their in depth I/O capabilities make them appropriate for parallel connections to a number of battery modules. Furthermore, they will expedite advanced calculations, resembling state-of-charge estimation, with effectivity.

The BMS Reference Design boasts a number of notable options. The design affords numerous {hardware} methods for SOC calculations. One technique employs the Nios II processor with floating-point acceleration. One other technique merges the Nios II with floating-point acceleration and a floating-point matrix processor. A 3rd technique blends the Nios II processor with the DEKF algorithm inside a devoted floating-point IP. Impressively, the system-in-the-loop simulation operates a MATLAB Simulink mannequin which communicates immediately with FPGA {hardware} by the Altera system console API. This setup facilitates real-time comparability of outcomes from the FPGA with these derived from Simulink calculations. Moreover, the Nios II processor manages scheduling and liaises with MATLAB by way of the System Console. Lastly, the operational backdrop for the Nios II software program is the μC/OS-II real-time working system.

This reference design comes with the Altera MAX 10 FPGA growth package (rev C). The BMS reference design necessitates particular software program parts for optimum performance. This consists of the Altera Full Design Suite model 15.0, encompassing the Quartus II software program v15.0, DSP Builder v15.0, and the Altera Nios II Embedded Design Suite (EDS) v15.0. Moreover, MATLAB R2015a can be required for the design’s operation. To learn extra about this reference design, click on right here.

[ad_2]